Recently, the paper titled "Identifying SAT Resilient Blocks through LUT Switching Analysis for Compound Logic Locking Schemes", with first author Wang Jianbin, a master's student (Class of 2023) from our school, has been accepted by FPL (International Conference on Field Programmable Logic and Applications), a top-tier conference in the field of programmable logic. Co-authors of the paper are Wang Xuelei, Zhang Xinyu, Tang Shibo, Zhou Huisi, and Hu Wei; the corresponding author is Professor Hu Wei. This paper marks the first publication by Northwestern Polytechnical University at the FPL conference, and all co-authors are affiliated with our university.

The FPL conference is the oldest and largest international conference in the field of programmable logic and reconfigurable computing, and is one of the top three premier conferences in this domain. Since its inception in 1991, FPL has promoted the innovative development of programmable logic and reconfigurable computing technologies. It has witnessed major breakthroughs over more than thirty years in areas such as reconfigurable architecture design, applications, embedded processing, and design automation. The full-paper acceptance rate has consistently been around 20%. The 35th FPL conference will be held in Leiden, Netherlands, in September 2025.

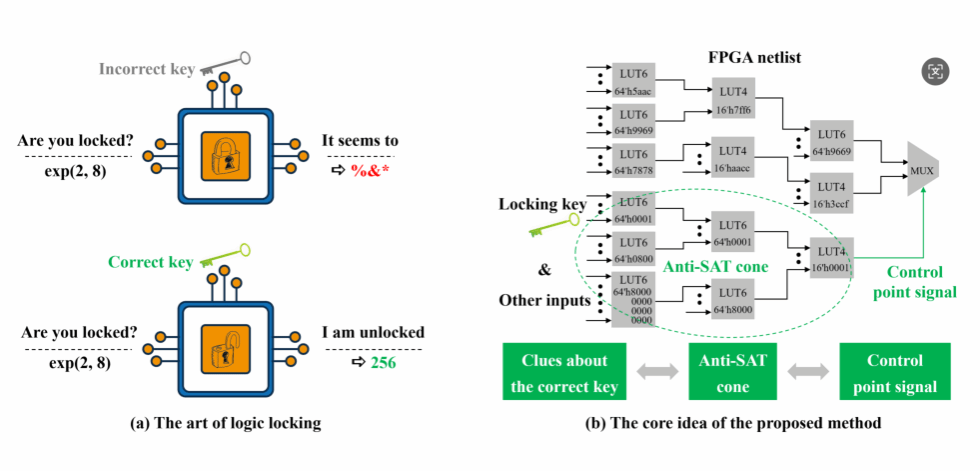

Addressing the latest and most secure compound logic locking scheme in the field of integrated circuit hardware security, this paper innovatively proposes a method for identifying Anti-SAT components and control point signals by analyzing the design structure and behavioral characteristics at the FPGA netlist level from the perspective of programmable logic. This approach aims to obtain critical clues about the locking key. The average success rate of the proposed method exceeds 90%, with the key recovery rate reaching 100%. Its outstanding performance provides an important technical reference for future security evaluation of logic locking schemes.

This research result originates from the Cryptography and Chip Security research team led by Professor Hu Wei. Centered on national strategies for cyberspace security and integrated circuits, the team focuses on the field of integrated circuit hardware security. It has achieved a series of innovative research results in areas such as security verification and vulnerability mining, fault diagnosis and fault tolerance, processor and system-on-chip security, and cryptography. These results have been successfully applied in the security evaluation and testing of chip designs for several companies. In terms of talent cultivation, team members have repeatedly achieved excellent results in high-level academic competitions, including the China Graduate Cybersecurity Innovation Challenge, the First National Integrated Circuit Security Challenge, and mathematical modeling competitions.